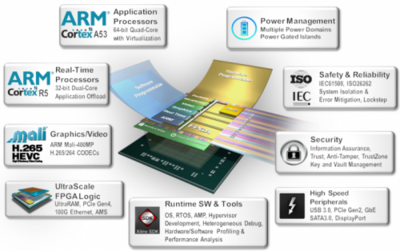

隨著嵌入式系統向高性能、高集成度、高靈活性的方向發展,異構計算與全可編程架構的結合已成為前沿趨勢。米爾科技推出的MYD-CZU3EG開發套件,正是這一趨勢下的杰出代表。它搭載了Xilinx Zynq UltraScale+ MPSoC系列中極具代表性的XCZU3EG芯片,將ARM Cortex-A53多核應用處理器、Cortex-R5實時處理器與Artix架構的可編程邏輯(FPGA)緊密集成,為開發者提供了一個功能強大且極具靈活性的軟硬件協同開發平臺。本文將從應用軟件開發的視角,深度解析這套“奢華”套件的開發體驗、潛力與挑戰。

一、 開發環境搭建:專業與便捷的平衡

MYD-CZU3EG的軟件開發根植于強大的Xilinx Vitis統一軟件平臺。對于應用軟件開發者而言,起點通常是基于Vitis或Petalinux構建定制的Linux操作系統鏡像。套件提供的豐富資料,包括原理圖、PCB文件及預編譯的鏡像,極大降低了入門門檻。開發者可以快速在SD卡上啟動一個功能完整的Ubuntu或Petalinux系統,并通過千兆以太網、USB、UART等接口與開發板交互。

真正的“奢華”體驗在于其深度定制能力。開發者可以利用Petalinux工具鏈,從內核驅動、設備樹到根文件系統進行全方位裁剪與配置,以精確匹配特定應用的需求。Vitis平臺則進一步將ARM側的裸機或Linux應用開發、FPGA側的硬件加速內核(通過HLS或RTL開發)以及兩者間的通信(如AXI總線)整合在同一個工程中,實現了真正的軟硬件協同設計與調試。

二、 異構編程模型:釋放硬件潛力的關鍵

MYD-CZU3EG的核心魅力在于其異構架構。應用軟件開發不再局限于ARM處理器,而是需要考慮如何高效利用FPGA可編程邏輯作為硬件加速單元。

- 標準應用開發:對于運行在Cortex-A53 Linux環境的上層應用,開發體驗與通用ARM開發板類似。開發者可以使用C/C++、Python等語言,調用豐富的開源庫,開發圖形界面(通過板載HDMI)、網絡服務或文件操作等應用。強大的四核A53處理器為復雜的算法和多媒體處理提供了充足的算力基礎。

- 硬件加速集成:當遇到性能瓶頸(如圖像處理、加密解密、實時信號處理算法)時,開發者可以將計算密集型函數通過Vitis HLS(高層次綜合)或傳統的Vivado HDL流程,實現為FPGA硬件加速IP核。通過Vitis提供的XRT(Xilinx Runtime)API,在主機(ARM)應用程序中,可以像調用動態庫一樣輕松地調用這些加速內核,并管理數據傳輸(通過PL側的DDR控制器或高效AXI接口)。這種“主控+加速”的模式,能帶來數十倍甚至更高的能效比提升。

- 實時處理與低延遲控制:Cortex-R5核心的存在,為時間關鍵型任務(如工業通信協議棧、電機控制)提供了安全的隔離運行環境。開發者可以編寫裸機或基于FreeRTOS的實時程序,與A53上運行的非實時Linux系統并行不悖,并通過片上存儲器或寄存器進行低延遲通信。

三、 應用場景與開發實例

得益于其全可編程的靈活性,MYD-CZU3EG套件在多個領域具有廣闊的應用前景:

- 機器視覺與AI邊緣計算:在ARM端運行OpenCV或深度學習推理框架(如TensorFlow Lite),同時將圖像預處理(如去噪、畸變校正)或特定算子(如卷積)在FPGA中硬化,實現高速、低功耗的視覺處理流水線。

- 高速通信與網絡處理:利用FPGA實現自定義的網絡協議棧、數據包過濾或高速接口(如Camera Link),由ARM進行上層協議解析與控制,非常適合5G前傳、工業網關等設備。

- 高端儀器與控制系統:結合R5核的實時性和FPGA的精確時序控制能力,開發數字電源、電機驅動或自動化測試設備。

以一個簡單的圖像濾鏡加速為例,開發流程可概括為:在Vitis HLS中編寫灰度轉換或邊緣檢測算法并生成IP -> 在Vivado中搭建ARM與FPGA的互聯系統 -> 使用Vitis編譯生成FPGA比特流和ARM端可執行文件 -> 在MYD-CZU3EG板上,通過XRT API將圖像數據發送至FPGA加速并取回結果。整個過程體現了軟硬協同的完整閉環。

四、 挑戰與思考

盡管功能強大,但MYD-CZU3EG的開發也面臨一些挑戰:

- 學習曲線陡峭:開發者需要同時理解嵌入式Linux、ARM多核編程、FPGA設計以及異構通信機制,對知識和技能棧要求較高。

- 調試復雜性:軟硬件聯合調試,尤其是追蹤數據在PS(處理系統)與PL(可編程邏輯)之間的交互,需要熟練使用Vitis Analyzer、邏輯分析儀(ILA)等高級工具。

- 資源權衡:如何在有限的PL資源(XCZU3EG的Logic Cells約15.4萬)、功耗和性能之間取得最優平衡,是設計中的永恒課題。

五、

米爾MYD-CZU3EG開發套件絕非普通評估板,它是一個面向未來復雜嵌入式系統的“全功能實驗室”。在應用軟件開發層面,它提供了從傳統嵌入式Linux到前沿軟硬件協同計算的平滑過渡路徑。其“奢華”之處不僅在于硬件配置的豪華,更在于它賦予開發者的一種“終極控制權”——能夠根據應用需求,從晶體管級到應用軟件層,自由地定義和優化整個計算架構。對于追求極致性能、能效和靈活性的研發團隊而言,深入掌握MYD-CZU3EG的軟件開發,無疑是搶占下一代智能設備制高點的關鍵一步。它不僅是開發工具,更是實現創新思想的強大畫布。